Поберегись, ARM? Новые 64-разрядные ядра Synopsys ARC увеличат производительность втрое

Немногие знают, что процессорная архитектура ARC является одной из самых распространенных архитектур наряду с ARM, MIPS и x86. Разработанная в 1980-х годах, архитектура ARC применяется в различных контроллерах для широчайшего спектра высокотехнологичной продукции, а каждый год на основе ARC производится около 1,5 миллиарда устройств.

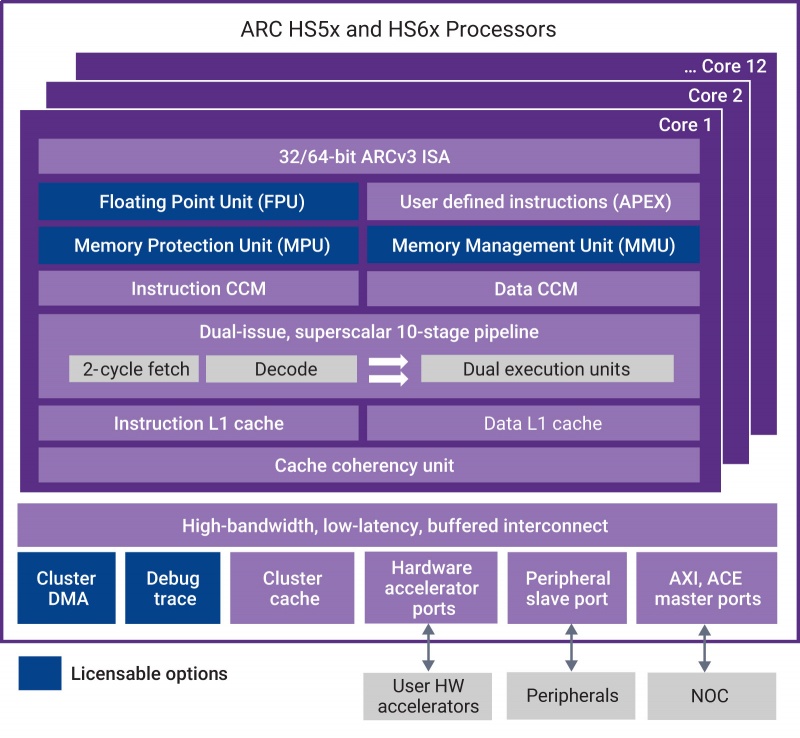

На днях корпорация Synopsys анонсировала новое поколение 32- и 64-разрядных процессорных ядер ARC, которые обещают увеличить производительность по сравнению с предшественниками втрое, а также позволят строить системы-на-кристалле с 12 ядрами. Таким образом, новые ядра позволят Synopsys конкурировать с ARM в ряде новых направлений.

"Встраиваемые приложения вроде контроллеров для твердотельных накопителей или сетевого оборудования становятся все более сложными, что требует значительного увеличения производительности при ограниченном энергопотреблении и форм-факторов", - сказал Джон Кетер (John Koeter), старший вице-президент по маркетингу и стратегии в области интеллектуальной собственности в Synopsys. "С выпуском новой архитектуры ARCv3 и ядер ARC HS5x и HS6x разработчики смогут удовлетворить растущие требования к производительности своих SoC сегодня и в будущем".

Новые семейства процессоров Synopsys DesignWare ARC включает в себя 32-разрядные ядра HS56/HS57D/HS58 и 64-разрядные ядра HS66/HS68. Свежеанонсированные процессоры предназначены для широкого круга приложений, таких как контроллеры для твердотельных накопителей (SSD), сетевые контроллеры, автопилоты для транспортных средств, информационно-развлекательные системы для автомобилей и многих других. Принимая во внимание растущие требования к объемам оперативной памяти, 64-разрядные ARC HD6x позволят создавать системы с 4,5 Пбайт DRAM, в то время как устройствам на базе ARC HD5x придется ограничиться меньшими объемами. Впрочем, реальные объемы поддерживаемой оперативной памяти скорее будут продиктованы используемой операционной системой, а видимые преимущества 64-разрядных CPU - более широким конвейером и большим файлом регистров.

Что касается архитектур DesignWare ARC HS5x и DesignWare ARC HS6x, то они поддерживают набор команд ARCv3, который может быть расширен инструкциями APEX (ARC Processor EXtensions), если кому-то из клиентов понадобиться нечто специфическое. Кроме того, ARC HS57D оснащается цифровым сигнальным процессором ARCv3DSP с поддержкой 150 команд. Новые ядра имеют глубину конвейера в 10 ступеней, могут исполнять две инструкции за такт, а также экипированы 128-разрядным модулем операций с плавающей запятой. При этом, наиболее продвинутые версии ядер поддерживают кеш второго уровня (L2) размером до 16 Мбайт.

Если говорить о производительности, то Synopsys заявляет про 3 DMIPS на МГц в целочисленных вычислениях, а также 5,1 CoreMark на МГц, что очень неплохо для миниатюрных ядер с минимальным энергопотреблением. Так, 3 DMIPS на МГц - это выше, чем у довольно мощных процессоров Cortex-A55, тогда как 5,1 CoreMark на МГц - выше, чем у любого процессора ARM для микроконтроллеров.

| Процессорные ядра Synopsys DesignWare ARC HS5x и HS6x | |||||

| HS5x | HS6x | ||||

| HS56 | HS57D | HS58 | HS66 | HS68 | |

| Набор команд | ARCv3 | ||||

| Инструкции APEX | Поддерживаются | ||||

| Разрядность | 32-разряда | 64-разряда | |||

| Инструкций за такт | 2 | ||||

| Длина конвейера | 10 ступеней | ||||

| DSP | - | ARCv3DSP 150 инструкций | - | - | - |

| Точность FPU | FP16, FP32, FP64 | ||||

| Процессорный кластер | 12 ядер | ||||

| Ускорителей на кластер | 16 ускорителей | ||||

| L1 | Кеш инструкций + Кеш данных | ||||

| L2 | - | - | 16 Мбайт | - | 16 Мбайт |

| Максимальный объем памяти | 64 Гбайт (зависит от ОС) | 4,5 Петабайт | |||

| Частота (на т/п 16FFC) | 1,8 ГГц | ||||

| DMIPS | 5400 DMIPS на ядро / 3 DMIPS на МГц | ||||

| CoreMark | 9180 CoreMark на ядро / 5,1 CoreMark на МГц |

Одной из ключевых особенностей нового семейства DesignWare ARC HS5x и DesignWare ARC HS6x является возможность создавать системы-на-кристалле (system-on-chip, SoC) с 12 процессорными ядрами общего назначения и 16 специализированными ускорителями. Каждое ядро/ускоритель в таком процессоре работает на собственной тактовой частоте и использует собственную подсистему питания для максимизации энергоэффективности. Наряду с новыми ядрами Synopsys также предлагает и внутрипроцессорное кеш-когерентное соединение со скоростью передачи данных 800 Гбайт/с.

Подобного рода SoC на базе архитектуры ARC не очень распространены сегодня, но принимая во внимание перспективные процессоры для систем автопилотирования, хранения данных, управления потоками данных, многоядерность и разного рода ускорители придутся очень кстати. Последнее даст возможность Synopsys конкурировать с ядрами ARM за место место в SoC для указанных приложений, чего не случалось до сих пор. Так, ядрами DesignWare ARC HS5x и DesignWare ARC HS6x уже заинтересовался производитель твердотельных накопителей Starblaze.

"Разработчики высокопроизводительных встраиваемых решений постоянно сталкиваются с новыми вызовами в сфере достижения высокой производительности при использовании больших объемов памяти и ограничениями в области энергопотребления и размеров", - сказал Брюс Чен (Bruce Cheng), главный научный сотрудник Starblaze. "Возможности новых 32-разрядных процессоров ARC HS5x и 64-разрядных процессоров HS6x компании Synopsys в области многоядерности позволят нам перейти на новый уровень эффективности энергопотребления, который не предлагается другими процессорами, представленными на рынке в настоящее время".

Synopsys начнет предлагать ядра ARC HS56, HS57D, HS58, HS66, HS68, а также их мультипроцессорные версии HS56MP, HS57DMP, HS58MP, HS66MP, HS68MP, начиная с третьего квартала 2020 года. Кроме того, компания предложит пакет ARC MetaWare Development Toolkit для создания микросхем на базе указанных ядер, а также симулятор и верификатор для проверки работоспособности SoC перед воплощением в кремнии. Что касается поддержки со стороны операционных систем, то новые ядра будут совместимы с рядом дистрибутивов Linux, Zephyr, а также разного рода фирменными ОС.