Intel делится подробностями о Sapphire Rapids, Tiger Lake и Alder Lake

Каждое новое поколение микропроцессоров корпорации Intel получает различные расширения набора инструкций для архитектуры x86. Новые команды призваны увеличить производительность с помощью использования параллелизма на уровне данных (с применением SIMD-инструкций), либо за счет специализированных аппаратных блоков. На днях Intel опубликовала новый документ для разработчиков программного обеспечения, где раскрыла подробности о новых инструкциях, поддерживаемых выходящими в ближайшие годы процессорами Sapphire Rapids, Tiger Lake, и Alder Lake. Характер новых команд может дать некоторое представление о приоритетах Intel при разработке будущих CPU.

Производительность и безопасность

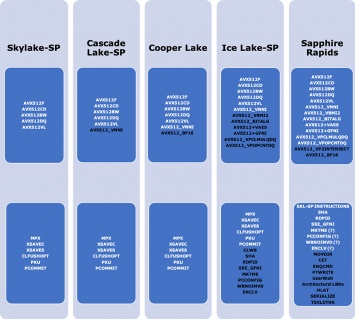

Традиционно новые инструкции направлены на два основных направления: увеличение производительности при обработке крупных массивов данных и/или при шифровании/дешифровании данных, а также внедрение новых технологий в области криптографии/безопасности. Крупные массивы данных редко обрабатываются на процессорах для клиентских ПК, а требования к безопасности персональных компьютеров и серверов весьма разнятся. Как следствие, внедряемые расширения набора инструкций x86 различаются в случае ядер для потребительских и серверных CPU. Ниже мы попытались проиллюстрировать эволюцию внедрения новых инструкций для процессоров Intel Xeon Scalable и Intel Core последних и будущих поколений.

Одним из основных двигателей прогресса Intel области производительности в последние годы стал набор инструкций AVX-512, впервые появившейся в CPU поколения Skylake-SP. Данные инструкции стали поддерживаться массовыми клиентскими процессорами лишь с появлением микроархитектуры Ice Lake, так как физическая реализация 512-разрядного файла регистров существенно увеличивает размер ядра (до 15 % в случае ядра Skylake), а сами блоки потребляют большое количество энергии (что требует снижения тактовой частоты процессора при использовании AVX2/AVX-512) и требуют высокой пропускной способности памяти.

Основным отличием эволюции AVX-512 от предшественников является то, что Intel пошла по пути внедрения специфических команд для узкоспециализированных приложений, а не создания универсальных команд, пригодных для широкого спектра программ. Так, по заявкам крупных клиентов Intel, процессоры поколения Cascade Lake-SP получили инструкции AVX512_VNNI для многократного ускорения вычислений, связанных с глубоким обучением. Кроме того, процессоры Cooper Lake получат команды AVX512_BF16 для матричных вычислений в формате BFLOAT16. Впрочем, судя по всему, Cooper Lake не получат действительно широкого распространения.

Таким образом, до последнего времени большинство команд AVX-512 поддерживалась исключительно ядрами Intel для серверных процессоров. При этом ряд других инструкций - главных образом из области безопасной обработки данных - для серверных и клиентских процессоров также различен.

Ice Lake-SP: максимальные изменения со времен Skylake-SP

Как неоднократно отмечалось, 10-нм процессоры поколения Ice Lake принесли максимальные изменения как в области микроархитектуры, так и в области иных возможностей со времен Skylake.

Судя по документации Intel, серверные и потребительские ядра поколения Ice Lake будут иметь очень много общего в том, что касается поддержки инструкций AVX-512. Так, Ice Lake-SP получат поддержку инструкций AVX512_VBMI2, AVX512_BITALG, AVX512+VAES, AVX512+GFNI, AVX512+VPCLMULQDQ и AVX512_VPOPCNTDQ. Помимо указанных, клиентские ядра Ice Lake приобретут еще и AVX512_VNNI. Судя по всему, в Intel считают, что характер рабочих нагрузок в новых ПК будет таковым, что система команд AVX с вектором длиной 512 разрядов принесет существенную пользу, несмотря на увеличенные размер ядер, требования к пропускной способности памяти и энергопотребление.

При этом Ice Lake/Ice Lake-SP не будут поддерживать AVX512_BF16, что станет прискорбным фактом для тех, кто оперирует данными в формате BFLOAT16. Не совсем ясной остается судьба команд AVX512VBMI и AVX512IFMA, поддерживаемых Cannon Lake (как следствие, в иллюстрации они публикуются со знаком вопроса).

Что, возможно, более важно, так это то, что Ice Lake-SP получит поддержку таких технологий, как MKTME (Multi-Key Total Memory Encryption, шифрование памяти), ENCLV (инструкции для работы SGX в условиях высочайшей нагрузки), SHA (аппаратное ускорение SHA-алгоритмов), Fast Short REP MOV (увеличенная производительность переноса данных) и CLWB (cache line write-back without flush, которая требуется для лучшей работы с накопителями данных). В том, что касается шифрования содержимого памяти, процессоры AMD EPYC имеют неоспоримое преимущество перед Intel Xeon Scalable, а потому внедрение аналогичной технологии увеличит конкурентоспособность последних CPU.

Sapphire Rapids: возвращение AVX512_BF16

Процессоры Intel Xeon Scalable поколения Sapphire Rapids в первую очередь будут использованы в суперкомпьютере Aurora в конце 2021 года, а потому ничего удивительного, что они также приобретут поддержку AVX512_BF16 и AVX512_VP2INTERSECT (ускорение работы с векторными операциями). Кроме того, новые CPU обещают использование новой микроархитектуры, памяти типа DDR5. Что касается суперкомпьютера Aurora, то там процессоры Sapphire Rapids будут работать в паре с графическими процессорами для центра обработки данных Ponte Vecchio.

Кроме того, Sapphire Rapids получит целый ряд иных инструкций для увеличения производительности, таких как Architectural LBRs (Last Branch Recording), ENQCMD (часть инициативы по ускорению потокового перемещения данных Intel DSA) и HLAT (Hypervisor-managed Linear Address Translation).

Кроме того, Sapphire Rapids имеет ряд нововведений в области безопасности. Пожалуй, главная из них - команда SERIALIZE, которая форсирует очистку всех кешей и окончания исполнения буферизированных операций записи перед началом исполнением команды. В некотором роде это отказ от параллельного исполнения операций с целью бороться с уязвимостями вроде Spectre и Meltdown. Помимо этого, процессор будет поддерживать технологию Control-flow Enforcement (CET), а также инструкцию TSXLDTRK (прекратить/возобновить TSX load tracking) для технологии Intel TSX.

Tiger Lake: новая микроархитектура и Xe графика в конце 2020 года

Процессоры для потребительских ПК поколения Tiger Lake являются прямыми потомками Ice Lake, которые будут базироваться на микроархитектуре Willow Cove, иметь увеличенный до 3 Мбайт кеш третьего уровня на каждое ядро, а использовать графическое ядро на базе архитектуры Xe, а также поддерживать интерфейс PCIe 4.0.

Данные CPU не принесут существенных нововведений в области поддержки инструкций AVX, однако поддержат технологию Control-flow Enforcement (CET) и команду MOVDIR. Впрочем, усовершенствованная микроархитектура, увеличенные кеши, а также новый графический процессор и сами по себе являются обещают быть значимыми усовершенствованиями.

Появление Tiger Lake ожидается к концу этого года, а потому нет ничего удивительного в том, что процессоры данного поколения будут поддерживать ряд команд Sapphire Rapids.

Alder Lake: наследники Tiger Lake

Клиентские процессоры Alder Lake в первый раз упоминаются компанией Intel официально. Судя по всему, они сменят Tiger Lake в конце 2021 года и будут поддерживать инструкции Architectural LBR, HLAT (Hypervisor-managed Linear Address Translation), а также SERIALIZE. При этом не совсем понятно, будет ли Alder Lake поддерживать CET и MOVDIR.

Как видно, Intel продолжает расширять набор команд AVX-512 для процессоров Xeon Scalable, а также добавляет поддержку части этих команд в ядра для потребительских CPU. Судя по всему, в Intel предполагают, что задачи для клиентских ПК вскоре потребуют подходов к вычислениям похожих на те, что применяются в серверах и суперкомпьютерах.

Примечательно, что Intel внедряет целый ряд набор технологий, направленных на увеличение безопасности вычислений. Найденные в последние годы уязвимости микропроцессоров заставили Intel перестраховываться и внедрять дополнительные меры защиты в будущих CPU.