IBM уменьшит длину транзисторов вдвое

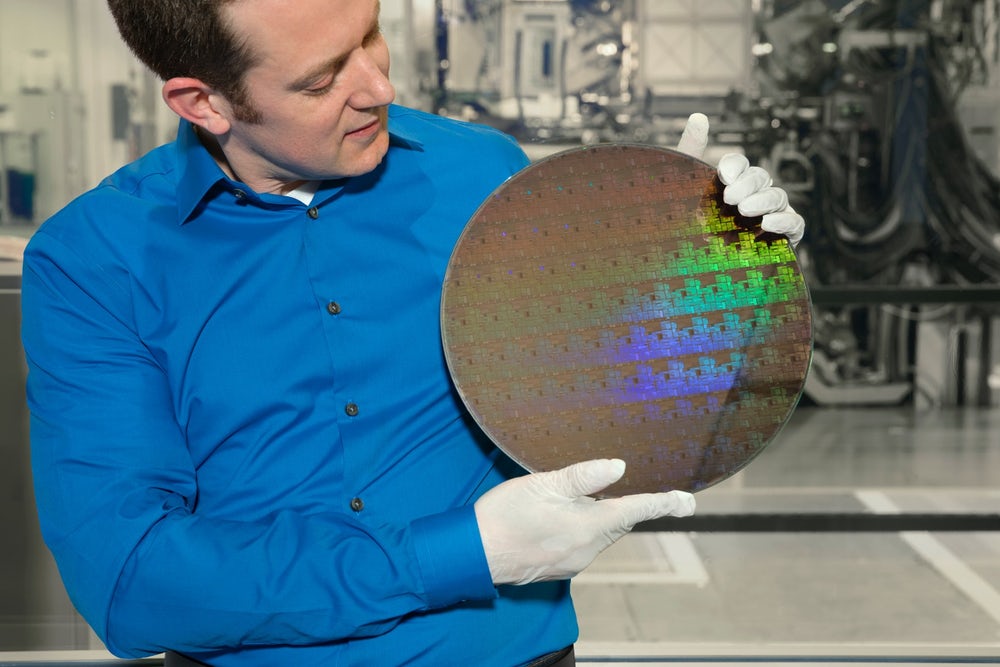

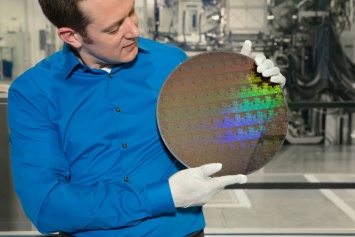

На данный момент длина серийных продвинутых транзисторов достигает 10 нм, в то время как стандартная длина 14 нм, а компания IBM хочет сократить их длину в половину и создать чип размером с ноготь, на который можно поместить 30 миллиардов транзисторов, что даст значительный прирост в эффективности.

Еще в 2015 году компания представила тестовый 7 нм транзистор, и тестовый чип размером с ноготь вмещающий 20 миллиардов транзисторов. Ожидается, что этот вид транзисторов и чипов появится на рынке уже в 2019 году.

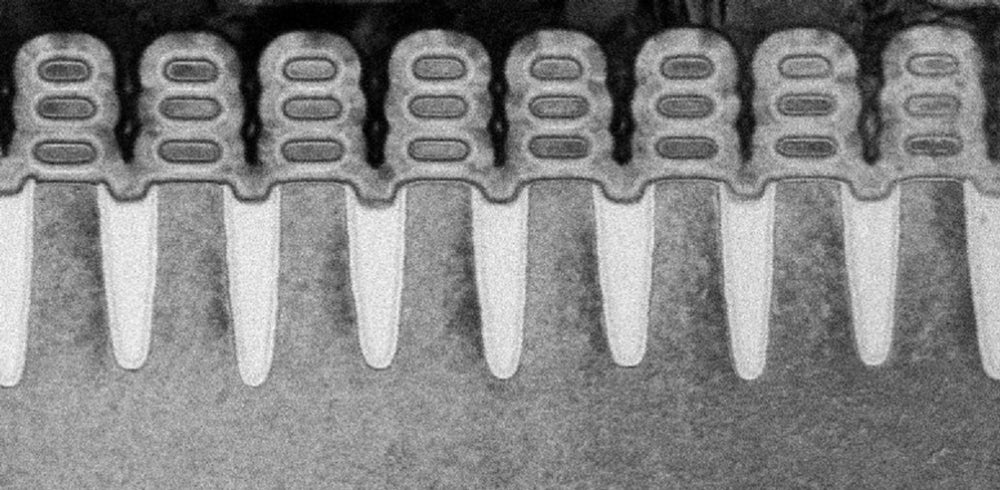

Теперь группа компаний представила следующий шаг в уменьшении размеров транзисторов, и хотя технически сократить размеры до 5 нм возможно, разработчики решили поменять архитектуру. Примерно с 2011 года при создании транзисторов использовалась FinFET архитектура, где транзисторы имели три токопроводящих канала окруженных изолированным слоем. Вместо этого, 5 нм чипы будут производиться с использованием сложенных кремниевых нанопластин, которые могут отправлять сигналы через четыре выхода, а не три как раньше.

Они созданы с использованием экстремальной ультрафиолетовой литографии, процессе, при помощи которого пишутся картины по кремниевым пластинам, он использует волны света с гораздо более высокой энергией. Это означает, что на чипе могут быть созданы мелкие детали, что добавит мощности.

5 нм прототипы способны улучшать производительность на 40 процентов от установленной мощности, их развитие может привести к меньшим, более мощным и более эффективным устройствам. Но выйдут они на рынок только после выхода 7нм транзисторов в 2019 году, примерно в 2023 году.